-

하태준 교수(전자재료공학과) 연구팀, 이황화 텅스텐 단분자층 기반 전계 효과 트랜지스터 제작 및 논리회로 개발

조회수 4075 | 작성일 2024.08.22 | 수정일 2024.08.22 | 홍보팀

-

하태준 교수(전자재료공학과) 연구팀, 산화 알루미늄 도핑 및 이중 게이트 구조를 이용하여

이황화 텅스텐 단분자층 기반 전계 효과 트랜지스터 제작 및 논리회로 개발

- 재료과학 분야에서 최상위 국제 학술지인 ACS Nano 논문 게재 (IF: 17.1, JIF ranking: 94.3%) -

(좌) 석박사 통합과정 박상준, 하태준 교수

본교 하태준 교수(전자재료공학과) 연구팀은 이화여대 곽준영 교수 및 연세대 장지원 교수 연구팀과 함께 화학 기상 증착법을 통해 성장시킨 tungsten disulfide (WS2) 단분자층을 채널층으로 이용하여 산화 알루미늄 도핑 및 산화 하프늄 기반의 이중 게이트 구조를 기반으로 낮은 문턱전압 이하 스윙 및 높은 전압 이득을 가지는 전계 효과 트랜지스터를 제작하고 논리회로를 구현하는데 성공하였다. 이번 연구 결과는 American Chemical Society에서 발행하는 재료과학 분야에서 최상위 국제 학술지인 ACS Nano (IF: 17.1, JIF ranking: 94.3%)에 “Realization of Extremely High-Gain and Low-Power in nMOS Inverter Based on Monolayer WS2 Transistor Operating in Subthreshold Regime” 제목으로 게재되었다.

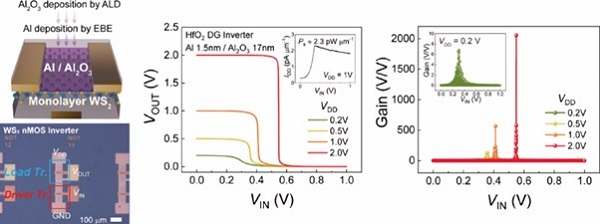

최근 기존 실리콘 대비 매우 얇은 두께를 가지는 2차원 전이금속 디칼코겐화물 물질이 전계 효과 트랜지스터의 스케일링을 위해 채널층으로서 많은 주목을 받고 있다. 그러나, 얇은 두께로 인해 동작 시 게이트 누설 전류가 크고 전하 산란 효과로 인해 게이트 제어성이 좋지 못한 문제점이 있다. 이에 하태준 교수(전자재료공학과) 연구팀은 이화여대 곽준영 교수 및 연세대 장지원 교수 연구팀과 함께 산화 알루미늄 도핑 및 산화 하프늄 기반의 이중 게이트 구조를 이용하여 낮은 문턱전압 이하 스윙 및 높은 전압 이득을 가지는 WS2 전계 효과 트랜지스터를 제작하였고 이를 통해 인버터를 구현하는데 성공하였다. 제작된 WS2 전계 효과 트랜지스터는 약 1010의 높은 on/off ratio 및 88 mV/dec의 낮은 문턱전압 이하 스윙을 보였다. 또한, 이를 기반으로 최대 2056이라는 높은 전압 이득과 약 2.3 pWm-1이라는 매우 낮은 전력을 보이는 NMOS 인버터 논리회로를 구현하는데 성공하였다.

한편, 이번 연구는 교내 대학혁신 미래도전 사업으로 하태준 교수가 연구소장으로 있는 인터렉티브 디스플레이 중점연구센터에서 공동 연구를 통해 얻은 성과이며, 광운대학교 교내학술연구비 지원 사업으로 수행되었다. 하태준 교수 연구팀은 첨단 재료를 기반으로 차세대 전자 소자 설계 뿐만 아니라 공정 개발에 대한 폭넓은 연구를 진행하고 있으며, 탄소 나노 튜브, 그래핀, 2차원 전이금속 디칼코겐화물 등의 차세대 반도체를 기반으로 한 연구로 60여편의 SCI 저널 게재 및 30여건의 국제/국내 특허 실적을 가지고 있다.

산화 알루미늄이 도핑된 WS2 전계 효과 트랜지스터 및 이를 이용한 인버터 성능 분석