-

채주형 교수 연구팀, DRAM의 테스트 신뢰성을 높이기 위한 회로설계기술 개발

조회수 662 | 작성일 2023.11.06 | 수정일 2023.11.06 | 홍보팀

-

채주형 교수 연구팀(전자통신공학과)

DRAM의 테스트 신뢰성을 높이기 위한 회로설계기술 개발

- IEEE Transactions on Instrumentation and Measurement (IF: 5.6, JCR: 86.5%)에 논문 게재 -

본교 채주형 교수 연구팀(전자통신공학과)은 DRAM 양산 테스트 과정 중 하나인 저속 웨이퍼 테스트 신뢰성을 높이기 위한 회로설계기술 개발에 성공했다.

웨이퍼 테스트에서는 DRAM 셀 및 회로의 불량을 검출하며 이를 위해서는 측정 장비와 DRAM 셀 간의 안정적인 테스트 패턴 및 결과들이 서로 송수신되어야 한다. 따라서 이러한 경로에 배치되어 있는 회로에서 테스트 중 예기치 못한 오동작을 일으키게 되면 테스트의 신뢰성이 떨어지게 되고 잘못된 테스트 결과를 얻을 수 있다. 일반적으로 DRAM I/O 회로는 고속으로 동작하기 때문에 설계 및 검증 시에 고속 동작에 초점을 맞추게 되는데 이 경우 저속으로 동작하는 웨이퍼 테스트 시에 예기치 못한 동작 불량이 발생할 수 있다. 채주형 교수 연구팀은 테스트 경로 상의 고속 동작을 위한 클럭 기반 샘플러에서 발생하는 저속 불량 현상을 발견 및 이를 개선하기 위한 회로설계기술을 제안하고 개발하였다.

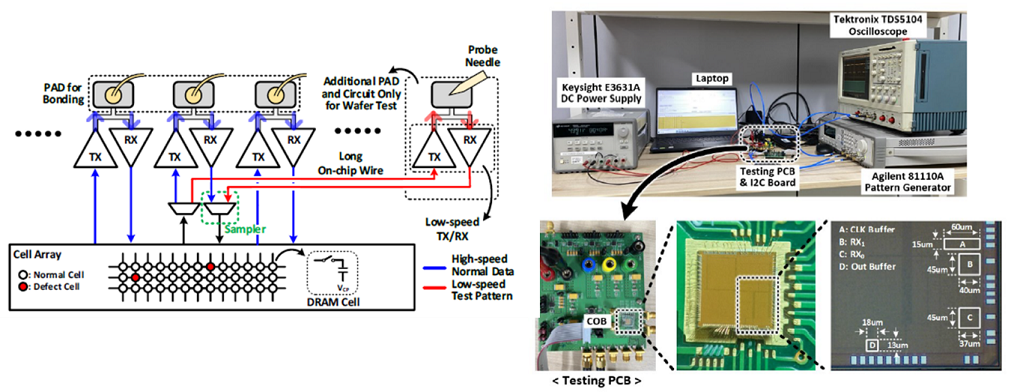

CMOS 공정을 사용하여 제안하는 회로설계기술을 적용한 프로토타입 IC 칩을 제작한 후 오동작 현상의 재현과 제안하는 아이디어를 사용하여 개선된 결과를 직접 검증하였다. 해당 기술이 DRAM I/O 회로 및 관련 회로들에 적용되어 향후 여러가지 테스트의 신뢰성 향상에 기여할 것으로 기대된다.

본 연구는 정부(과학기술정보통신부)의 재원으로 정보통신기획평가원(IITP)의 “PIM 인공지능반도체 핵심기술개발 사업”(2022-0-01013; 엣지용 연산기능강화 DRAM PIM 반도체기술개발, 2022-0-01037; DRAM 기반 고성능 PIM 메모리 반도체 기술 개발), 한국연구재단(NRF)의 “무선이동체 미래선도 핵심기술개발사업”(NRF-2021M1B3A3102358; 433MHz 기반 드론 응용 통신 기술 개발 및 실증), 그리고 본교의 우수연구자지원사업의 지원으로 수행되었다. 연구결과는 국제저명학술지인 IEEE Transactions on Instrumentation and Measurement (IF: 5.6, JCR: 86.5%)에 “Design of Clocked Comparator Preventing Bit Errors to Improve Reliability of Low-Speed DRAM Measurement”의 제목으로 게재되었다.

*Web Link: https://doi.org/10.1109/TIM.2023.3318687

<DRAM Test Path와 테스트 신뢰성을 높이기 위한 회로설계기술이 포함된 프로토타입 IC 칩 및 검증을 위한 셋업>